4.5倍分頻

1.分頻原理

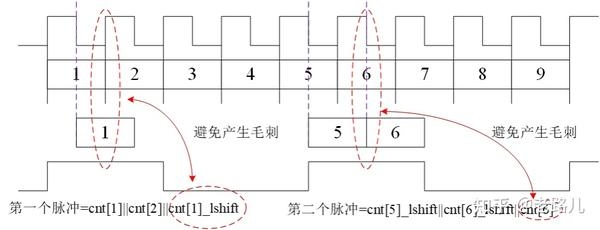

4.5倍分頻,相當於9個參考時鐘中包含兩個對稱的脈沖。

為瞭得到兩個對稱的脈沖,在第5個計時周期從下降沿采集,得到對稱的兩個4.5個周期。然後設計時鐘脈沖,保證兩邊對稱,即可在9個參考鐘內得到兩個對稱的脈沖。

4.5倍分頻原理

如圖所示,改變單邊時鐘脈沖即可得到任意占空比的小數分頻。以上示意圖中設計瞭44%和66%的占空比。

占空比44%

設計思路如下:

(1)設置9位移位寄存器,復位時為:1000_0000_0

(2)每個周期向左循環移位

(3)依次產生第一個脈沖clk_pulse1和第二個脈沖clk_pulse2

(4)最後輸出分頻後時鐘clk_out=clk_pulse1||clk_pulse2

占空比44%的4.5倍分頻時鐘

占空比44%的4.5倍分頻時鐘

需要註意的是,在這個設計中使用組合邏輯產生輸入時鐘,因此要避免毛刺的產生。

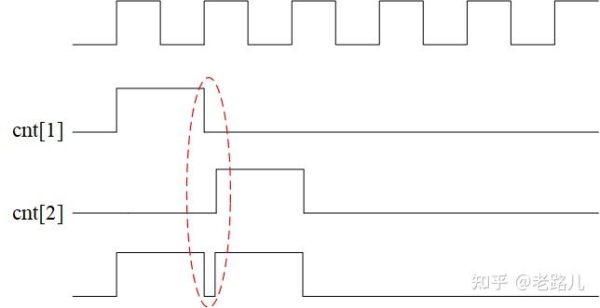

第一個脈沖clk_pulse1=cnt[1]||cnt[2]

在實際應用中,在cnt[1]寄存器拉低之後,cnt[2]由於某些電路原因延時一會兒才拉高(例如時鐘skew),那麼clk_pulse1=cnt[1]||cnt[2]就可能在cnt[1]和cnt[2]中間拉低,如圖所示:

毛刺產生

毛刺產生

因此為瞭避免這種情況的產生,將cnt[1]反轉180°,形成cnt[1]_lshift(在時鐘下降沿采集),因此clk_pulse1=cnt[1]||cnt[2]||cnt[1]_lshift。 同理可得clk_pulse2=cnt[5]_lshift||cnt[6]_lshift||cnt[6]。(其中cnt[6]為瞭避免毛刺的產生)。

占空比66%

占空比66%的4.5倍分頻時鐘

占空比66%相對於占空比44%的設計,在於將脈沖寬度擴大,同時引入兩處避免產生毛刺處。

2.代碼實現

占空比44%

`timescale 1ns/1ps

module fra_divclk_9(

input wire sclk,

input wire rst_n,

output wire clk_out

);

reg [9:1] div_cnt;

reg cnt1_lshift;

reg cnt5_lshift;

reg cnt6_lshift;

wire clk_pulse1;

wire clk_pulse2;

always @(posedge sclk or negedge rst_n)begin

if(rst_n==1'b0)begin

div_cnt<=9'b1000_0000_0;

end

else begin

div_cnt<={div_cnt[8:1],div_cnt[9]};

end

end

always @(negedge sclk or negedge rst_n)begin

if(rst_n==1'b0)begin

cnt1_lshift<=1'b0;//=div_cnt[1]

cnt5_lshift<=1'b0;

cnt6_lshift<=1'b0;

end

else begin

cnt1_lshift<=div_cnt[1];

cnt5_lshift<=div_cnt[5];

cnt6_lshift<=div_cnt[6];

end

end

assign clk_pulse1=div_cnt[1]||div_cnt[2]||cnt1_lshift;

assign clk_pulse2=cnt5_lshift||cnt6_lshift||div_cnt[6];

assign clk_out=clk_pulse1 || clk_pulse2;

endmodule